# MIXED SYMBOLIC-NUMERIC APPROACH FOR LARGE CIRCUIT SIMULATION

# Srdjan Djordjević, Predrag Petković

Faculty of Electronic Engineering, Beogradska 14, 18000 Niš, srdjandj@elfak.ni.ac.yu

Summary: This article suggests symbolic-numeric co-simulation as compromise approach that retains very important option of symbolic analysis — good insight into circuit behaviour, and efficiency of numerical analysis as well. For a set of circuits the proposed technique exhibited effectiveness in comparison with methods entirely based on numeric and on symbolic approaches. The approach will be illustrated on a benchmark example that will be analysed using all three methods. The obtained results will be compared in order to determine limitations in circuit topology and complexity for every approach.

# I. INTRODUCTION

Within the LEDA laboratory (Laboratory for Electronic Design Automation) at Faculty of Electronic Engineering in Niš, Yugoslavia, researches related to Symbolic analysis (SA) last more than a decade. As result three versions of program for symbolic circuit analysis [1-3] were developed.

This paper is focused to connection of symbolic and numeric approach within circuit analysis. In order to better understand all problems related to the subject the paper will start with a brief comparison between symbolic and numeric approach. These approaches explore advantage depending on circuit complexity. Therefore the idea is to employ each of them in the part where it is superior. This mixed approach is called *symbolic-numeric co-simulation*.

The method will be illustrated on a benchmark example.

The obtained results will be compared in order to determine limitations in circuit topology and complexity for symbolic, numeric and mixed approach. The final part of the paper summarizes results obtained so far indicating that symbolic-numeric cosimulation is suitable for large circuit analysis.

#### II. ADVANTAGES AND DRAWBACKS OF SYUMBOLIC SIMULATION

Two main advantages of symbolic circuit simulation comparing with numeric analysis are:

- insight into circuit behaviour;

- immunity on errors inherent to numerical methods.

Main drawbacks SA explores for complex circuits:

- circuit expressions become cumbersome;

- generating circuit expressions takes considerable computer time and memory.

Insight into circuit behaviour becomes less obvious if the number of symbolic terms increases. Bearing in mind that number of symbols exponentially grows with circuit complexity, it is evident that SA is not suitable for large circuit.

One of the powerful tools to cope with this problem is the approximation technique [2, 4].

Hierarchical techniques represent another approach that makes SA more effective [3,5-8] because it results with circuit functions in nested form.

Despite increased number of symbols within a network function expression one cannot speak about loosing insight into circuit performance as far as he may use computer to visualize influence of a particular parameter on the circuit behaviour.

The main purpose of circuit analysis is to expose response under different circumstances. When one wants to figure up how frequency affects output voltage, he runs one Spice AC analysis. The required time is relatively acceptable even for complex circuits. However, if he wants to trace effect of different circuit parameters on the circuit function, he needs to run repetitive analysis for different parameter values. Although one analysis does not require much time, the overall time may be considerable. The better insight one wants, more analysis are needed and much computer time is spent.

In contrary, symbolic analysis of complex circuits usually takes long time, but the result is very convenient for repetitive analysis. Further computation becomes as simple as calculating a formula value for given parameters. Obviously, numeric or symbolic approaches explore advantage depending on circuit complexity. The best is to employ each of them in the part where it is superior. This approach we call symbolic-numeric co-simulation (SNC).

# III. DEFFINITION OF SYMBOLIC-NUMERIC CO-SIMULATION

More than ten years ago it was suggested in [9] that the near future of symbolic computation rely on interconnection with numerical methods. The same statement stands for symbolic circuit analysis as well. Consequently idea arose to combine SA with numeric methods. Having in mind that the best insight into circuit behavior offer activities related to visualization of circuit response under different parameter values, one requires efficient methods for generating data that are suitable for graphic representation. Usually those are tables obtained after repeated analysis within a loop.

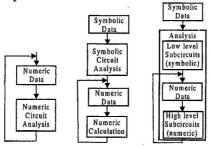

Fig. 1. illustrates differences between numeric, symbolic and mutual analysis during table generating. Within the loop, parameters values are changing.

The numeric approach requires repeating the overall analysis for every new data in the table.

Symbolic approach needs only one analysis and repetitive circuit function evaluation within the loop.

Fig. 1 Differences between three elaborated methods in scope of post-processing activities

As it was pointed out in the previous section, SA may be suitable for relatively small circuits while numeric methods are able to deal with larger, but still not without difficulties.

Considering that large circuits are easy to decompose in hierarchically ordered subcircuits it looks promising to use both approaches at levels where each of them is dominate. Therefore, the circuit functions of subcircuits at lowest level are determined symbolically. Afterward the analysis of the subnetworks at higher level is performed. This procedure consists of numeric determination of circuit response in terms of the previously generated functions in symbolic form.

Details of symbolic-numeric co-simulation (SNC) method are described in [10]. Determining the boundary between symbolic and numeric analysis is the most complex problem in practical application of SNC. It will be illustrated in the following example.

#### IV. PRACTICAL EXAMPLE

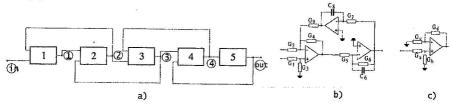

Figure 2 represents frequently used benchmark circuit [5-8] suitable for exploring many problems related to SA.

Fig. 2. Band-pass filter: a) block-diagram presentation, b) circuitry of blocks 1-4 c) circuitry of block 5

Analysis of the circuit when opamps where assumed as quasy-ideal building blocks showed that SNC has advantage comparing with pure numeric or pure symbolic analysis [10]. Table I summarised normalized computation times for all three analyses when the time spent for PSpice analysis was taken as reference. The analyses goal was to generate a table containing results for 100 different values of one circuit parameter for 100 points at frequency axe.

| Numeric<br>(PSpice) | Symbolic | SNC<br>0,47 |  |

|---------------------|----------|-------------|--|

| 1                   | 0,73     |             |  |

Table I: Time required for getting result in 100x100 table form

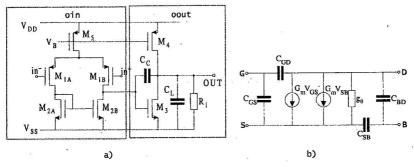

However, more precise analysis requires better opamp models. Therefore, every opamp in Fig. 2 was replaced by circuitry presented in Fig. 3.

Fig. 3. a) OPAMP used for filter in Fig.2 b) MOS transistor model

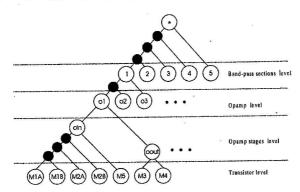

SA at transistor level requires circuit decomposition on smaller subcircuits. Figure 4 represents graph of hierarchical decomposed handpass filter. Every node corresponds to a subcircuit. The lowest decomposition level is transistor level ( $M_i$ , i=1,...,5). At the next level opamp is decomposed on input and output stages ( $o_{in}$ ,  $o_{out}$ ), as Figure 3.a indicates. The subsequently higher level is the opamp level ( $o_i$ , i=1,2,3) while the last level represents particular band-pass stages denoted with 1, ..., 5 as depicted in Fig. 2.a.

The same decomposition was performed for SNC, as well. Now, the major problem is proper choosing of boundaries between levels that are going to be processed by symbolic and numeric analysis.

In order to determine all dilemmas related to the topic we have done a set of different analyses.

There are three effects that contribute to the time needed for SNC, T<sub>SNC</sub>. Namely, those are:

• time spent for symbolic computation, T<sub>s</sub>;

- time spent for derivation semi-symbolic expressions, T<sub>d</sub>;

- time spent for numeric calculation,  $T_n$ ; and, consequently  $T_{SNC} = T_s + T_d + T_n$ .

Fig. 4 Hierarchical decomposition of the band-pass filter

Results obtained for case that SNC considers opamps at symbolic level (denoted as SNC<sub>opamp</sub>), and for case that symbolic analysis is performed one level lower and corresponds to input and output stages of the opamps (denoted as SNC<sub>OSL</sub>) are summarized in Table II.

|                                      | SNC (opamp) | SNC (OSL)    |  |

|--------------------------------------|-------------|--------------|--|

| T <sub>s</sub> /T <sub>SNC</sub> [%] | 18,10       | 6,35<br>7,12 |  |

| T <sub>d</sub> /T <sub>SNC</sub> [%] | 14,80       |              |  |

| T <sub>n</sub> /T <sub>SNC</sub> [%] | 67,10       | 86,52        |  |

Table II: Relative time required for getting result in 100x100 table form for band-pass filter analysed at transistor level

Obviously, increase of time spent for symbolic analysis reduces time needed for numeric analysis.

However, if complexity of symbolic expression describing lower hierarchical level growths, the number of multiplications at each interconnecting node rises and the overall computation time gets higher. This is illustrated in Table III where computation time is given in terms of the subcircuit transfer function order.

| order of transfer function | 3    | 7     | 11    | 15    |

|----------------------------|------|-------|-------|-------|

| SNC computation time [s]   | 7,84 | 20,16 | 30,31 | 38,15 |

Table III: SNC computation time in terms of interconnection transfer function order

#### v. CONCLUSION

This paper characterizes symbolic-numeric co-simulation of electronic circuits. Particular care was payed to determine limitations in circuit topology and complexity for symbolic, numeric and mixed approach.

In general there are three factors responsible for efficiency of symbolic-numeric

co-simulation.

Firstly, it is complexity of interconnects between neighbouring subcircuits. More connections between two subcircuits exist, the greater interconnecting circuitry is.

Secondly, if complexity of symbolic expression describing lower hierarchical level increases, the number of multiplications at each interconnecting node rises and the overall computation time gets higher.

Finally, the efficiency of SNC depends on circuit complexity reduction. Namely, the grater part of a circuit is replaced by transfer function, the greater benefits SNC explores.

# VI. REFERENCES

[1]P. Petković, V. Litovski, "Linear Circuit Analysis based on Symbolic Algebra", 15-16 Annual School on Semiconductor and Hybrid Technologies, 1992-1993, Sozopol, Bulgaria, May 1993, pp. 112-120.

[2]P. Petković, V. Živković, "Symbolic Approximation in Analogue Circuit Design", 18<sup>th</sup> International Spring Seminar on Semiconductor and Hybrid Technologies, 1995-6, Sozopol,

Bulgaria, pp. 275-284.

[3]S. Đorđević, P. Petković, "A hierarchical approach to large circuit symbolic simulation",

Microelectronic Reliability, Vol. 41, 2001., pp. 2041-2049.

[4] Katzenelson, J., and Unikovski, A., "Symbolic-Numeric Circuit Analysis or Symbolic Circuit Analysis with Online Approximations", *IEEE Tran. on CAS I: Fundamental Theory and Applications*, Vol. 46, No. 1, January 1999.

[5] Marwan M. Hassoun, Kevin S. McCarville "Symbolic analysis of large-scale networks using a hierarchical signal flowgraph approach", J. Analog VLSI Signal Process., vol. 3, Jan. 1993, pp.

31-42.

[6] Marwan M. Hassoun, Pen-Min Lin "A hierarchical network approach to symbolic analysis of large-scale networks" IEEE Trans. Circuits Syst., vol. 42, April 1995, pp. 201-211.

[7]X.-D. Tan, R. Shi, "Hierarchical Symbolic Analysis of Analog Integrated Circuits via Determinant Decision Diagrams", *IEEE Trans. On Computer Aided Design of Integrated Circuits and Systems*, Vol. 19, No. 4, April 2000, pp. 401-412.

[8]S.-J. Jou, M.-F. Perng, C.C. Su, "Hierarchical techniques for symbolic analysis of electronic circuits", IEE Proc. Circuits Devices Syst., Vol. 144, No. 3, June 1997, pp. 167-177.

[9]Boyle, A. and Caviness, B.F., editors, "Future Directions for Research in Symbolic Computation", SIAM-Society for Industrial and Applied Mathematics, Philadelphia, 1990.

[10] S. Dorđević, P. Petković, "Symbolic-Numeric Co-simulation of Large Analogue Circuits", Proc. 23<sup>rd</sup> Int. Conf on Microelectronics (MIEL2002), Vol 2, Niš, Yugoslavia, 12-15 May 2002, pp. 639-642.