## Fast ISA-Bus multi-channel analyzer

## Georgi Georgiev – INRNE - BAS Ivaylo Peev – Sofia University

## Abstract

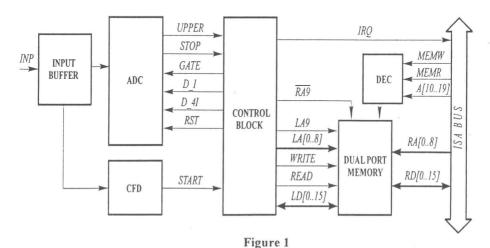

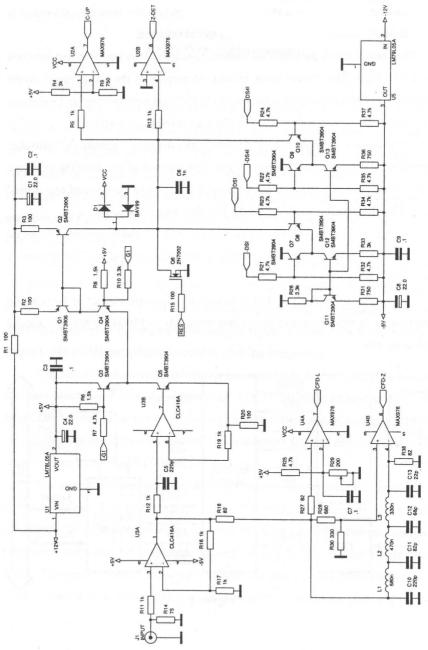

Fast nuclear spectroscopy multi-channel analyzer is described. It works with NaI(Tl) scintillation detectors at high-count rates and is performed as an ISA-Bus card. The module consists of an input buffer, constant-fraction discriminator, fast dual-slope ADC (gating integrator), control block, dual-port memory and high voltage power supply unit for photo-multipliers. Figure 1 is the block diagram of the analyzer and figure 2 shows the schematics of the input buffer, the constant-fraction discriminator and ADC.

The constant-fraction discriminator marks the occurrence of the input pulse independent of its rise time and amplitude. It uses a Bessel filter as a 30 ns delay line and two comparators. The first one is the level comparator. The second one is a zero-crossing comparator. It compares the delayed signal with the 30% fraction of it. The output pulse of this comparator is used to start the integration.

The fast dual-slope ADC integrates the input pulse in 1 us and has a maximum disintegration time of 4 us. It is a dual-scale ADC. If the input pulse is under ¼ of the range, the disintegration current is 250 uA instead of the nominal current of 1 mA. So the analyzer accumulates simultaneously two specters: one 256 channel (first ¼ of the range) and one 384 channel (the rest of the range).

The output signal of the input buffer is filtered using simple RC filter with 220 ns time constant. This time constant is near the decay time constant of the NaI(Tl) scintillator. The filtered signal is converted to current and this current charges the integrating capacitor C6 trough the current switch Q3Q4 and the current mirror Q1Q2. The current switch is opened 1 us after the start of the conversion. At the end of this time the control block checks the state of the comparator U2A and starts the

disintegration. It opens the switches Q7Q8 or Q9Q10. The comparator U2B works as a zero-crossing detector. When the voltage of C6 crosses the zero the conversion is done. The MOS transistor Q6 resets C6 after the conversion.

The control block performs all control functions. It is implemented into one Spartan 05 FPGA. The control block checks the outputs of the comparators, drives the current switches, accumulates the spectra in the dual-port memory and generates an interrupt request every 6 seconds. The clock frequency is 64 MHz.

The dual-port memory is split on two banks. Every 6 seconds the controller accumulates spectra into one of them. It uses both outputs of one flip-flop to switch between banks. The non-inverted output is used as LA9 and the inverted one is used as RA9. The other bank is visible from the ISA-Bus simultaneously.

The high voltage power unit delivers up to -2048 V and is software controlled using 12 bit DAC. This way it is possible to stabilize the spectra. The maximum output current is 2.5 mA.

The multi-channel analyzer has been used as ash-content meter of the coals on transport belts in thermal power plants and tested up to 160000 events per second output count rate.